Clock Status Monitor

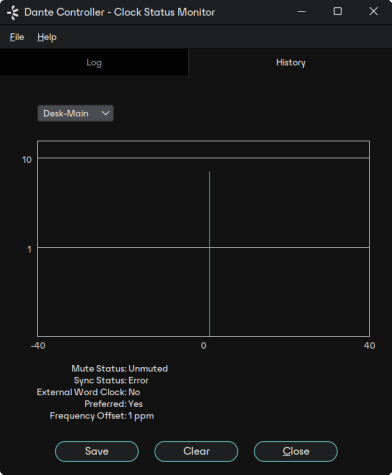

The Clock Status Monitor includes two tabs, Log and History.

Log

The Clock Status log shows time-stamped clock status events for each device that has been identified as unstable, or has lost or regained sync with the leader clock.

The event types are:

- Clock Sync Warning: Indicates that a clock has been identified as unstable, and is at risk of losing sync with the leader clock

- Clock Sync Unlocked: Indicates that a device has lost sync with the leader clock. This will result in the device being automatically muted until it regains sync.

- Clock Sync Locked: Indicates that a device has regained sync with the leader clock.

- Audio Mute: Indicates that a device was muted.

- Audio UnMute: Indicates that a muted device was un-muted.

To delete all Clock Status log entries, click Clear . This will reset the Clock Status Monitor icon to green.

Note: This will also clear all other event log entries (the Clock Status log is a filtered view of the main event log).

Dante Controller will then resume monitoring (unless the Clock Status Monitoring button is switched off).

To save the event log as an xml file, click Save.

History

The History tab can be used to establish the stability of device clocks. It shows a histogram of clock frequency offset for the selected device, and the current frequency offset value, updated in real time.

The following information is also displayed:

- Mute status

- Sync status

- External word clock

- Preferred leader status

About Clock Offset

Hardware clocks are based on a vibrating (piezoelectric) quartz crystal. All crystals are slightly different, and vibrate at slightly different frequencies. When a device ('follower') clock wants to sync to a leader network clock, its frequency must be 'pulled' up or down to match the frequency of the leader clock. The amount that the clock's frequency is pulled is referred to as 'offset'.

Hardware clocks can only support a certain amount of offset, referred to as 'pull range'. If the pull range is exceeded, the follower clock will lose sync with the leader clock, and the device will be automatically muted.

Software clocks typically use an algorithm to derive a clock from an internal counter. Software clocks can support any amount of offset.

Rapidly-changing offset can also cause a follower clock to lose sync with the leader clock.

Various factors can destabilise follower clocks by affecting their offset, such as:

- Overloaded network links

- Poorly-implemented EEE (Energy Efficient Ethernet)

- A leader clock that is derived from an inaccurate external word clock (one that does not run at its nominal frequency)

About the Histogram

The horizontal axis of the histogram shows the distribution of clock frequency offset measurements against the nominal frequency of the clock, in parts per million (ppm). The zero point of the horizontal axis corresponds to the clock's nominal frequency (i.e. the frequency that the clock is intended to run at - for example, 98kHz).

The vertical axis shows the number of measurements recorded at each data point, on a logarithmic scale.

The histogram is continually updated, with measurements taken roughly once per second.

- To select devices, click the drop-down menu at the top .

- To clear the histogram, click Clear.

- To save a png format screenshot of the current data, click Save.

Interpreting the Histogram

The histogram can be seen as an indication of how much work a follower clock is doing to stay in sync with the leader clock.

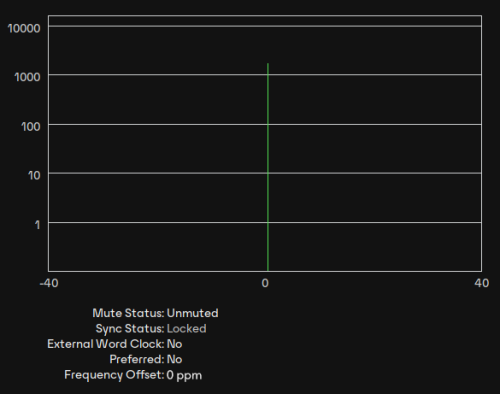

Generally, a stable and accurate clock will show consistently stable offset (with variation in the order of a few ppm). It means that it is not having to change its offset very much to stay in sync.

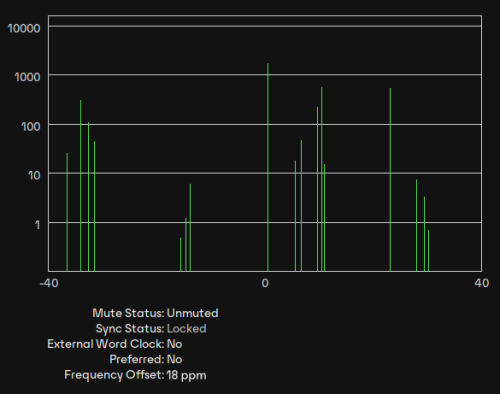

A histogram that shows a distributed range of offsets indicates an unstable clock - it is having to change its offset significantly, and often, to stay in sync with the leader clock. This can be due to overloaded network links, or poorly-implemented EEE. A device in this state is highly likely to lose sync with the leader clock.

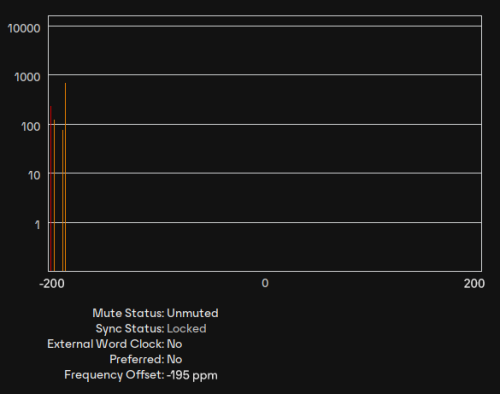

A histogram that shows measurements in amber and/or red indicates a clock that might be currently stable, but has little room for manoeuvre; its offset could easily move outside its pull range, at which point it will lose sync completely. This can result when the leader clock is derived from an inaccurate external word clock.

Note: Dante Controller can be left running for a few days (or even weeks) to collect clock status data, providing a long-term picture of the stability of your network clocking configuration.